2506/202 2507/202 ELECTRONICS AND CONTROL SYSTEMS Oct/Nov 2023 Time: 3 hours

## THE KENYA NATIONAL EXAMINATIONS COUNCIL

# DIPLOMA IN AERONAUTICAL ENGINEERING (AIRFRAMES AND ENGINES OPTION) (AVIONICS OPTION)

### **MODULE II**

#### **ELECTRONICS AND CONTROL SYSTEMS**

3 hours

#### **INSTRUCTIONS TO CANDIDATES**

You should have the following for this examination:

Answer booklet;

Mathematical tables / Non-programmable scientific calculator;

Drawing instruments.

This paper consists EIGHT questions in TWO sections; A and B.

Answer **THREE** questions from section A and TWO questions from section B in the answer booklet provided.

All questions carry equal marks.

Maximum marks for each part of a question are as indicated.

Candidates should answer the questions in English.

This paper consists of 9 printed pages.

Candidates should check the question paper to ascertain that all the pages are printed as indicated and that no questions are missing.

© 2023 The Kenya National Examinations Council

Turn over

## SECTION A: ELECTRONICS

Answer THREE questions from this section.

- 1. (a) Distinguish between:

- (i) intrinsic and extrinsic semiconductors;

- (ii) majority and minority charge carriers.

(4 marks)

(b) The voltage-ampere equation of a semiconductor diode is given by

$$i_D = I_0 \left( e^{\frac{V_D}{\eta V T}} - 1 \right)$$

- (i) Identify each parameter.

- (ii) Sketch the diode characteristic.

- (iii) Derive the expression for the dynamic resistance of the diode,

$$\frac{dV_D}{di_D}$$

(8 marks)

- (c) (i) With aid of a sketch, describe transistor load line and state its significance.

- (ii) Differentiate biasing of class A and class B push-pull transistor amplifiers.

(8 marks)

- 2. (a) Perform each of the following arithmetic operations in the given number systems:

- (i)  $(AFCD)_{16} + (9AAC)_{16}$ ;

- (ii)  $(467)_8 (276)_8$ ;

- (iii)  $0111\ 1001_{BCD} + 0011\ 0111_{BCD}$

(6 marks)

- (b) Simplify each of the following Boolean expressions:

- (i)  $(D+\overline{E})(D+E)$

- (ii)  $WXY + W\overline{X}Y + WX\overline{Y} + W\overline{X}\overline{Y}$ .

(6 marks)

- (c) Table 1 shows the truth table of a 2-bit multiplier with inputs  $A_1A_0$ ,  $B_1B_0$  and output  $P_3P_2$   $P_1P_0$ .

- (i) Complete the truth table.

- (ii) Draw a logic circuit diagram to implement the multiplier using 3-to-8 decoders and gates. (8 marks)

Table 1

| Input |       |       |       | Output |       |       |       |

|-------|-------|-------|-------|--------|-------|-------|-------|

| $A_1$ | $A_0$ | $B_1$ | $B_0$ | $P_3$  | $P_2$ | $P_1$ | $P_0$ |

| 0     | 0     | 0     | 0     | 0      | 0     | 0     | 0     |

| 0     | 0     | 0     | 1     | 0      | 0     | 0     | 0     |

| 0     | 0     | 1     | 0     | -      | _     |       | -     |

| 0     | 0     | 1     | 1     | 0      | 0     | 0     | 0     |

| 0     | 1     | 0     | 0     | 0      | 0     | 0     | 0     |

| 0     | 1     | 0     | 1     | 0      | 0     | 0     | 1     |

| 0     | 1     | 1     | 0     | -      | -     | -     | _     |

| 0     | 1     | 1     | 1     | 0      | 0     | 1     | 1     |

| 1     | 0     | 0     | 0     | 0      | 0     | 0     | 0     |

| 1     | 0     | 0     | 1     | _      | -     | _     | -     |

| 1     | 0     | 1     | 0     | 0      | 1     | 0     | 0     |

| 1     | 0     | 1     | 1     | 0      | 0     | 1     | 1     |

| 1     | 1     | 0     | 0     | 0      | 0     | 0     | 0     |

| 1     | 1     | 0     | 1     | -      | -     | _     |       |

| 1     | 1     | 1     | 0     | 0      | 1     | 1     | 0     |

| 1     | 1     | 1     | 1     | 1      | 0     | 0     | 1     |

# 3. (a) Define a transistor model.

(1 mark)

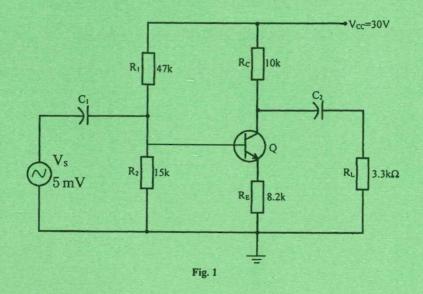

(b) Figure 1 shows a circuit diagram of a common-emitter amplifier. The silicon transistor Q has  $\beta=200$ ,  $V_{\rm BE}=0.7\,V$  and the resistance of the emitter diode  $r=\frac{25}{I_{\rm E}(mA)}\Omega$ .

2506/202 2507/202 Oct./Nov. 2023

| (i)        | Draw the equivalent circuit diagram of the amplifier.                                                                                                                                            |            |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| (ii)       | Determine the:                                                                                                                                                                                   |            |  |  |  |  |  |

|            |                                                                                                                                                                                                  |            |  |  |  |  |  |

|            | I. Thevenin input voltage;                                                                                                                                                                       |            |  |  |  |  |  |

|            | II. Thevenin input resistance;                                                                                                                                                                   |            |  |  |  |  |  |

|            | III. emitter-base diode resistance, $r_e$                                                                                                                                                        |            |  |  |  |  |  |

|            | IV. output a.c load resistance;                                                                                                                                                                  |            |  |  |  |  |  |

|            | V. voltage gain.                                                                                                                                                                                 | (13 marks) |  |  |  |  |  |

| Briefl     | y describe the working of each of the following display devices:                                                                                                                                 |            |  |  |  |  |  |

| (i)        | cathode ray tube (CRT);                                                                                                                                                                          |            |  |  |  |  |  |

| (ii)       | liquid crystal display (LCD). (6 marks)                                                                                                                                                          |            |  |  |  |  |  |

| Defin      | e each of the following with respect to analog-to-digital converters (AD                                                                                                                         | OCs):      |  |  |  |  |  |

| (i)        | conversion speed;                                                                                                                                                                                |            |  |  |  |  |  |

| (ii)       | monotonicity.                                                                                                                                                                                    |            |  |  |  |  |  |

| With       | aid of a block -schematic diagram, describe the counter-based ADC.                                                                                                                               | (6 marks)  |  |  |  |  |  |

|            | KX8 RAM is made from 8KX8 RAM chips. The RAM memory starts ss 1000H.                                                                                                                             | form       |  |  |  |  |  |

| (i)        | Determine the:                                                                                                                                                                                   |            |  |  |  |  |  |

|            | I. number of RAM chips required;                                                                                                                                                                 |            |  |  |  |  |  |

|            | II. memory address range of each RAM chip;                                                                                                                                                       |            |  |  |  |  |  |

|            | III. size of decoder required.                                                                                                                                                                   |            |  |  |  |  |  |

| (ii)       | Draw a schematic block diagram of the memory implementation.                                                                                                                                     | (12 marks) |  |  |  |  |  |

| A 32 addre | KX8 RAM is made from 8KX8 RAM chips. The RAM memory starts ss 1000H.  Determine the:  I. number of RAM chips required; II. memory address range of each RAM chip; III. size of decoder required. | form       |  |  |  |  |  |

5. transistors (BJTs). (3 marks)

2506/202 2507/202 Oct JNov. 2023

(c)

(a)

(b)

(c)

4.

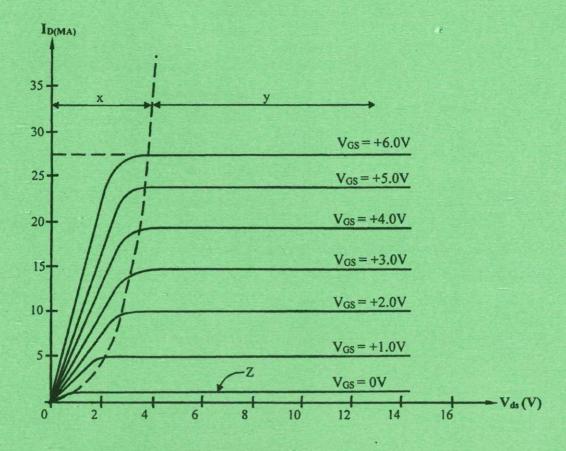

(b) Figure 2 shows the characteristic curve of a MOSFET.

Fig. 2

- (i) Identify the regions labelled x, y and z and explain their significance.

- (ii) Distinguish between enhanced and depletion modes of operating MOSFETs. (8 marks)

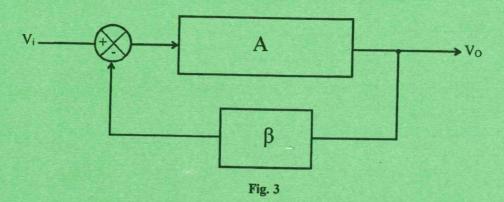

(c) Figure 3 shows a block diagram of a negative feedback amplifier where A is the gain without feedback and  $\beta$  is the feedback factor.

- (i) Derive the expression of the gain with feedback.

- (ii) An amplifier has a gain of 1000 and a negative feedback of 0.22. Determine the voltage gain with feedback.

- (iii) State three effects of negative feedback on an amplifier. (9 marks)

### **SECTION B: CONTROL SYSTEMS**

Answer TWO questions from this section.

6. (a) A control system is described by the following open-loop expression.

$$G(s) = \frac{10(s+2)(s-4)}{s(s+1)(s+3)}$$

- (i) Determine the:

- I. poles;

- II. zeros.

- (ii) Sketch the poles and zeros on a s-plane.

- (iii) State with reasons the stability of the system.

(9 marks)

(b) A unity feedback system has an open-loop transfer function

$$G(s) = \frac{k}{s(s+10)}$$

- (i) Determine the:

- I. characteristic equation;

- II. value of k so that the system will have a damping ratio of 0.5.

- (ii) For this value of k determine, for a unit step input, the:

- I. settling time;

- II. percentage peak overshoot.

(11 marks)

- 7. (a) With aid of block diagrams, describe each of the following:

- (i) transfer function;

- (ii) series compensation.

(6 marks)

(b) A signal flow graph is described by the following linear equations:

$$y = y_1 + \alpha \cup$$

$$\dot{y}_1 = -\beta y_1 + y_2 + \alpha_2 \cup$$

$$\dot{y}_2 = -\beta_2 y_1 + \alpha \cup$$

- (i) Determine the transfer function of the equations using Laplace transforms.

- (ii) Draw the signal flow diagram.

- (iii) Using Mason's rule, determine the transfer function of the system.

(14 marks)

- 8. (a) State **two** advantages of servomotors over stepper motors with respect to control system. (2 marks)

- (b) A unity feedback control system is described by the open-loop transfer function:

$$G(s) = \frac{k}{s(s^2 + 2s + 2)(s^2 + 6s + 10)}$$

Determine each of the following with respect to root locus:

- (i) the zeros;

- (ii) the poles;

- (iii) centroid;

- (iv) asymptotic angles.

(8 marks)

2506/202 2507/202 Oct /Nov. 2023

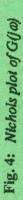

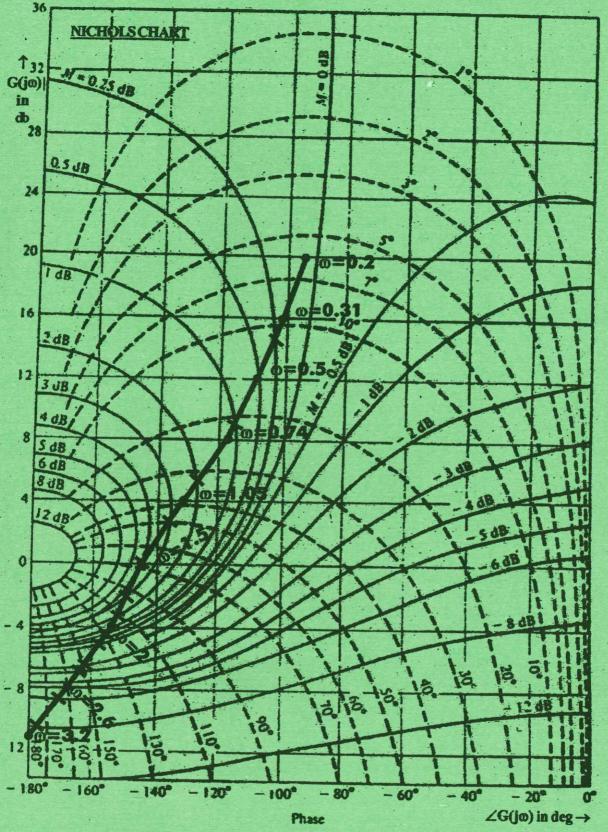

- Figure 4 shows a Nichols plot for a control system. Determine the: (c)

- (i) (ii) phase margin; gain margin;

- (iii) peak value of closed-loop gain response, Mp;

- (iv) resonant frequency;

- (v) bandwidth.

(10 marks)

THIS IS THE LAST PRINTED PAGE.

2506/202 2507/202 Oct /Nov. 2023